Em 21 de junho, na Conferência de Sistemas de Acionamento Elétrico e Fórum da Indústria de Motores de Acionamento SMM (4ª) 2025 - Fórum de Sistemas de Acionamento Elétrico para Automóveis, organizada conjuntamente pela SMM Information & Technology Co., Ltd. (SMM), Hunan Hongwang New Material Technology Co., Ltd., Governo Popular do Distrito de Louxing e Zona de Desenvolvimento Econômico e Tecnológico de Loudi de nível nacional, Zhong Jingwen, especialista em módulos de acionamento da Joyee Powertrain Systems Co., Ltd., compartilhou insights sobre o tema "Plano de Desenvolvimento Tecnológico para Blocos de Inversores de Controle Elétrico".

I. Planejamento de Blocos de Inversores

II. Exibição de Blocos de Inversores Gen1

Exibição de Blocos de Inversores Gen1 (Segmento de Baixa Potência TPAK)

Ele também analisou conteúdos como Exibição de Blocos de Inversores Gen1 (TPAK Paralelo no Segmento de Potência Média), Exibição de Blocos de Inversores Gen1 (HPD no Segmento de Alta Potência) e Exibição de Blocos de Inversores Gen1 (Controle Elétrico Duplo).

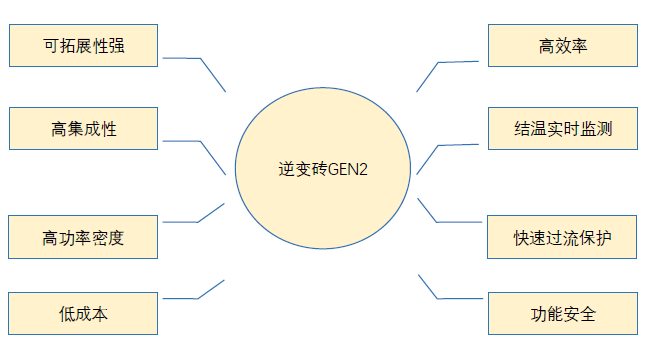

III. Exibição de Blocos de Inversores Gen2

Análise de Demanda de Blocos de Inversores Gen2

Requisitos para Melhoria do Desempenho de Blocos de Inversores Gen2:

• Baixa indutância parasitária para reduzir perdas de comutação e adaptar-se a aplicações SIC;

• Design baseado em plataforma com alta compatibilidade (plataforma de tensão, SIC & IGBT);

• Melhoria da precisão e eficácia do monitoramento da temperatura de junção;

• Proteção rápida contra sobrecorrente para adaptar-se a aplicações SIC;

• Dissipação eficiente de calor e alta densidade de potência;

• Resistência à temperatura aprimorada da junção do módulo de potência;

• Otimização de custos.

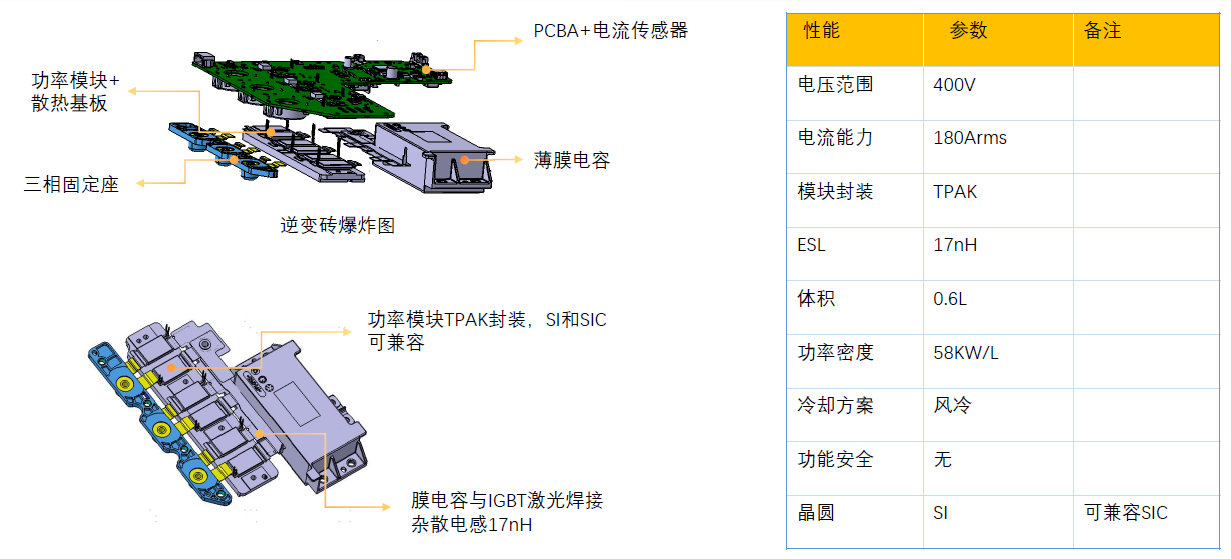

Blocos de Inversores Gen2

Blocos de Inversores para Plataforma de Potência Média (<150kW):

• Compatível com plataformas de 400V e 800V;

• Compatível com módulos de potência IGBT e SIC.

Blocos de Inversores para Plataforma de Potência Alta (<250kW)

• Compatível com plataformas de 400V e 800V;

• Compatível com módulos de potência IGBT e SIC.

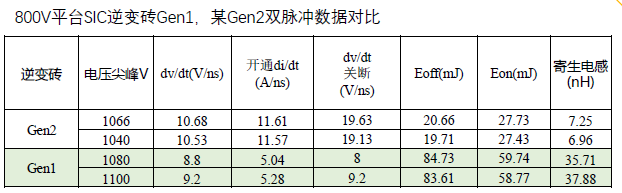

Blocos de Inversores Gen2 - Design de Baixa Indutância Parasitária e Encapsulamento Integrado de Capacitores

Design de Baixa Indutância Parasitária: Design otimizado de barramento e núcleo para capacitores DC-Link, com indutância parasitária controlada em <2nH; processo de soldagem a laser utilizado para conexões terminais do módulo de potência, com indutância parasitária total controlada em <5nH.

Resinagem Integrada de Capacitores: Os capacitores de ligação CC e os canais de água da carcaça são resinados integralmente, reduzindo eficazmente os custos, minimizando o tamanho e melhorando as capacidades de dissipação de calor do núcleo.

• A indutância parasitária do sistema de bloco inversor Gen2 pode ser reduzida para 8nH, uma redução de 75% em relação ao Gen1; sob o mesmo pico crítico de tensão, as perdas de comutação são reduzidas em 70%, melhorando significativamente a eficiência e a capacidade de saída dos módulos SIC.

Bloco Inversor Gen2 - Módulo de Potência

Detecção Integrada de Corrente Sem Núcleo: Um esquema de detecção sem núcleo é utilizado para a amostragem de corrente trifásica, eliminando os núcleos tradicionais e reduzindo eficazmente os custos dos sensores; a redução do tamanho do núcleo e o uso de soldagem a laser para barramentos de cobre trifásicos podem encurtar eficazmente as dimensões dos terminais trifásicos.

Compatibilidade: Compatibilidade com pacotes IGBT e SIC; compatibilidade com pacotes de plataformas de 800V e 400V.

Plataforma de alta potência - HPD G3: 470V@≥560Arms; 900V@≥460Arms; Tjmax 185°C@SIC.

Plataforma de média potência - HPD SMALL: 470V@≥560Arms; 900V@≥320Arms; Tjmax 185°C@SIC.

Suporte à detecção de temperatura no chip: Suporta a capacidade de detecção de temperatura no chip, permitindo o monitoramento rápido, direto e eficaz da temperatura de junção e a execução de proteção.

Suporte à detecção de sobrecorrente no chip: Os módulos SIC têm menor capacidade de resistência a curto-circuitos; o suporte à detecção de sobrecorrente no chip permite uma proteção rápida contra condições de sobrecorrente e curto-circuito.

Exibição do Bloco Inversor Gen3 (Tecnologia de Embalagem Integrada em PCB)

Introdução à Solução Técnica:

A indutância parasitária do módulo integrado é de aproximadamente 3nH, a indutância parasitária do sistema integrado é de aproximadamente 6-8nH; a indutância parasitária do pacote HPD é de aproximadamente 8-10nH; a indutância parasitária do sistema HPD é de aproximadamente 25nH-30nH.

As perdas dinâmicas são reduzidas em aproximadamente 50% em relação ao sistema HPD, com um aumento de 20% na saída de corrente para a mesma área do chip.

Custo total do módulo: A embalagem integrada pode reduzir os custos em aproximadamente 10-20%, principalmente devido à economia na área do chip. (Pré-requisito: Melhoria no rendimento do processo de embutimento de PCB para atingir os níveis de rendimento de produção em massa de PCB convencionais.)

Custo do sistema de controle elétrico: Com o aumento da densidade de potência e da integração, há uma oportunidade para reduzir ainda mais o custo do sistema de controle elétrico.

Display do Inverter Brick Gen3 (Tecnologia de Embalagem Embutida em PCB)

Clique para visualizar o Relatório Especial da Conferência de Sistemas de Acionamento Elétrico e Fórum da Indústria de Motores de Acionamento 2025SMM (4ª edição)